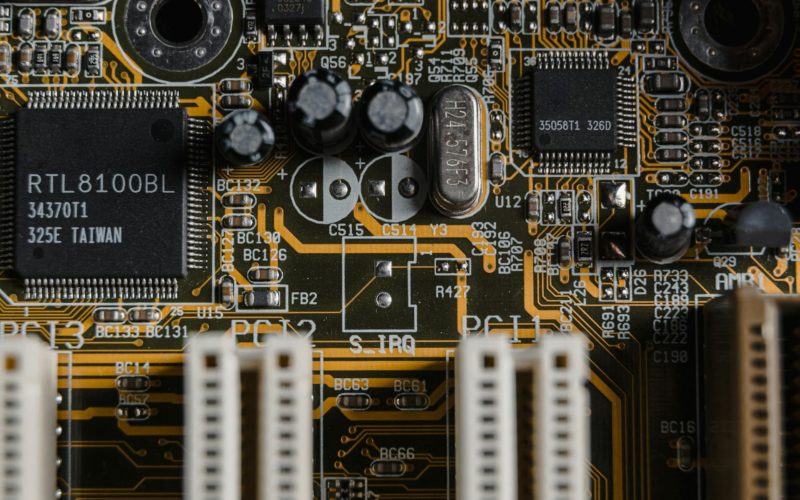

Printed circuit boards (PCBs) serve as the backbone of electronic devices. Designers often overlook hidden pitfalls that cause signal issues, delays, or extra costs. Errors can occur at the schematic capture, layout, or fabrication stages. Spotting these problems early saves time and budget. The cost of a single board spin may exceed small teams’ development budgets, which is why flexible circuit board manufacturers emphasize thorough design reviews before fabrication. Even large firms seek to cut rework cycles. This guide highlights 10 common PCB design mistakes. Each point offers clear advice to fix issues before production.

1. Incorrect footprint and land pattern

Using the wrong footprint or land pattern leads to solder bridges or open joints. Manufacturers publish precise land patterns. Always match pad size and spacing to component datasheets. A tiny mismatch can cause poor solder flow.

Refer to IPC-7351 guidelines for footprint geometry, which cover secondary and generic shapes. Many CAD tools include built-in libraries that comply with these standards. Customize footprints only after testing mask layers thoroughly. In addition, export mask layers and verify pad alignment against the board outline. These steps reduce assembly failures.

2. Inadequate trace width and spacing

Thin traces can overheat or fail under high current, and narrow gaps risk short circuits. Before routing, review PCB design rules from your fabrication house. Use calculators to determine the proper trace width for the current load. Be sure to follow the manufacturer’s minimum spacing guidelines to avoid arcing and crosstalk. Adjust parameters for high‑voltage or high‑speed signals.

In addition, you should keep consistent spacing between differential pairs. Be sure to also use teardrops at pad‑to‑trace junctions to strengthen connections and prevent cracking.

3. Poor component placement

Effective component placement influences signal flow, reduces trace length, and minimizes noise. You should group related parts to minimize routing complexity and improve performance. Be sure to place decoupling capacitors close to power pins, and avoid clustering heat-sensitive parts near hot components. Ensure test points are accessible for probes.

In addition, you should balance component density to ease soldering and inspection. Be sure to keep keep‑out areas clear for connectors and mechanical fixtures. You should also review placement with mechanical and thermal teams before routing.

4. Neglecting signal integrity

Ignoring reflections and impedance mismatches leads to data errors on high‑speed lines. Define controlled impedance traces for critical nets like USB, Ethernet, or LVDS. Use proper stack‑up to maintain a consistent dielectric constant. Route differential pairs side by side with correct gap.

You should also avoid stubs or right angles in signal paths. Be sure to simulate key nets early to check signal behavior. Eye diagrams help verify timing margins. Be sure to also address signal integrity before prototyping. This prevents redesigns after boards arrive.

5. Ignoring thermal management

High‑power components need heat dissipation to stay within safe temperature limits. Place thermal vias under power ICs to conduct heat to inner planes or heatsinks. Be sure to keep copper pour areas around hot parts for heat spread. Add thermal relief on pads to balance solderability with heat transfer.

In addition, you should avoid placing heat sources too close to temperature‑sensitive parts. Be sure to simulate board temperature using thermal analysis tools. Early layout decisions save time on thermal testing. Proper thermal planning ensures long device life.

6. Inadequate power and ground planes

Split or missing planes cause voltage drops and ground loops. Use a solid ground plane to provide low‑impedance return paths. Be sure to place the power plane adjacent to the ground plane in the stack‑up for capacitance.

In addition, you should avoid splitting planes under high‑speed nets. Route all power rails with sufficient copper weight, and stitch planes with vias to reduce loop area. Be sure to also ensure that every component pad has a direct connection to the plane. A well‑designed plane network simplifies routing and improves EMC performance.

7. Overlooking DFM guidelines

Skipping design for manufacturability (DFM) checks invites unwanted surprises during fabrication. Each board house defines limits for drill sizes, annular rings, and solder mask clearance. Ignoring these specs can lead to misdrills, solder bridging, or warped panels.

Be sure to review the fab’s design checklist early in layout. Confirm clearance rules for V‑scoring or mouse bites when depanelizing. In addition, ensure traces and pads stay clear of board edges and tooling holes. You can consult manufacturers on panel and test‑coupon placement. Early feedback prevents production holds and extra charges.

8. Insufficient decoupling and bypassing

Skipping decoupling capacitors leads to noise on power rails. Place capacitors as close as possible to supply pins. Use a mix of values, for example, 0.1 µF and 10 µF, to cover different frequency ranges. You should also route capacitor connections with short traces to the ground plane. Be sure to check library parts for correct ESR and ESL specifications, as well as cluster decouplers around critical ICs. Poor bypassing can cause jitter or even device resets.

9. Skipping design rule checks

Relying on manual checks alone invites mistakes. Run a design rule check (DRC) in your CAD tool after each major layout change. Set rule parameters based on your chosen fabricator’s specs. Be sure to inspect flagged violations such as spacing or copper pour errors.

Additionally, you should use ERC and LVS tools to validate connectivity. Be sure to automate batch checks for multi‑board projects. Treat DRC warnings seriously, and only ignore them when you fully understand the implications. A clean DRC report saves time and money.

10. Inconsistent silkscreen and documentation

Mixed-up silkscreen layers confuse assembly and testing teams. Keep reference designators clear and oriented consistently, and avoid printing silkscreen on pads or vias. Ensure polarity marks and pin‑one indicators are visible. Be sure to also update documentation to reflect component substitutions or footprint changes.

Additionally, you should provide complete fabrication and assembly drawings. Poor documentation can lead to misplacement and rework. A clear silkscreen enhances production quality and reduces errors.

Endnote

Avoiding these common PCB design mistakes leads to smoother production. Early planning and rule adherence reduce rework costs. Consistent collaboration with manufacturing partners helps clarify requirements. Be sure to use automated tools to enforce checks and catch errors. You should also document your design thoroughly for future revisions.

In addition, educate your team on best practices, including layout reviews and signal integrity testing. Regularly update CAD libraries and fabrication guidelines. You should also prioritize both functionality and manufacturability from day one. Following these steps supports reliable boards, faster time to market, and happier customers.